# ICF 9000

# **Standard**

InnoDisk

**Approver**

| Customer:    |  |

|--------------|--|

| Customer     |  |

| Part Number: |  |

| InnoDisk     |  |

| Part Number: |  |

| InnoDisk     |  |

| Model Name:  |  |

| Date:        |  |

|              |  |

**Customer**

**Approver**

# the total solution for industrial flash storage

### **Table of contents**

| 1. | INTRODUCTION9 |        |                                                             |    |  |  |  |

|----|---------------|--------|-------------------------------------------------------------|----|--|--|--|

| 2. | FEATU         | JRES.  |                                                             | 9  |  |  |  |

| 3. | PIN AS        | SSIGN  | IMENT                                                       | 11 |  |  |  |

| 4. | PIN DI        | ESCR   | IPTION                                                      | 13 |  |  |  |

| 5. | SPECI         | FICA   | FIONS                                                       | 17 |  |  |  |

|    | 5.1           | CE A   | AND FCC COMPATIBILITY                                       | 17 |  |  |  |

|    | 5.2           | RoH    | IS COMPLIANCE                                               | 17 |  |  |  |

|    | 5.3           | Envi   | RONMENTAL SPECIFICATIONS                                    | 17 |  |  |  |

|    | 5.            | 3.1    | Temperature Ranges                                          | 17 |  |  |  |

|    | 5.            | 3.2    | Humidity                                                    | 17 |  |  |  |

|    | 5.            | 3.3    | Shock and Vibration                                         | 17 |  |  |  |

|    | 5.            | 3.4    | Mean Time between Failures (MTBF)                           | 17 |  |  |  |

|    | 5.4           | MEC    | HANICAL DIMENSIONS                                          | 18 |  |  |  |

|    | 5.5           | ELEC   | CTRICAL SPECIFICATIONS                                      | 19 |  |  |  |

|    | 5.5.1         | DC (   | CHARACTERISTIC                                              | 19 |  |  |  |

|    | 5.5.2         | Тіміг  | NG SPECIFICATIONS                                           | 19 |  |  |  |

|    | 5.            | 5.2.1  | True IDE PIO Mode Read/Write Timing Specification           | 19 |  |  |  |

|    | 5.            | 5.2.2  | True IDE Multiword DMA Mode Read/Write Timing Specification | 20 |  |  |  |

|    | 5.            | 5.2.3  | True IDE Ultra DMA Mode Data Burst Timing Specification     | 21 |  |  |  |

|    | 5.6           | TRAI   | NSFER FUNCTION                                              | 23 |  |  |  |

|    | 5.            | 6.1    | True IDE Mode I/O Transfer Function                         | 23 |  |  |  |

|    | 5.7           | Con    | FIGURATION REGISTER                                         | 24 |  |  |  |

|    | 5.7.1         | Con    | FIGURATION OPTION REGISTER (200H IN ATTRIBUTE MEMORY)       | 24 |  |  |  |

|    | 5.7.2         | Pin I  | REPLACEMENT REGISTER (204H IN ATTRIBUTE MEMORY)             | 25 |  |  |  |

|    | 5.7.3         | Soc    | KET AND COPY REGISTER (206H IN ATTRIBUTE MEMORY)            | 25 |  |  |  |

|    | 5.8           | Sof    | TWARE INTERFACE                                             | 26 |  |  |  |

|    | 5.8.1         | Trui   | E IDE MODE ADDRESSING                                       | 26 |  |  |  |

|    | 5.            | 8.2 CI | F-ATA Register                                              | 26 |  |  |  |

|    | 5.9           | HAR    | DWARE RESET                                                 | 31 |  |  |  |

|    | 5.10          | Pow    | /ER ON RESET                                                | 31 |  |  |  |

|    | 5.11          | SUPI   | PORT IDE COMMANDS                                           | 32 |  |  |  |

|    | 5.11.1        | Сне    | CK POWER MODE -E5H                                          | 33 |  |  |  |

|    | 5.11.2        | EXE    | CUTE DEVICE DIAGNOSTIC - 90H                                | 33 |  |  |  |

|    | 5.11.3        | FLUS   | SH CACHE- E7H                                               | 34 |  |  |  |

|    | 5.11.4        | IDEN   | TIFY DEVICE- ECH                                            | 35 |  |  |  |

|    | 5.11.5        | IDLE   | -97H or E3H                                                 | 45 |  |  |  |

|    |               |        |                                                             |    |  |  |  |

| 7. | INNODISK PART NUMBER RULE              | 74 |

|----|----------------------------------------|----|

| 6. | DEVICE PARAMETERS                      | 73 |

|    | 5.11.29 SMART DISABLE OPERATIONS       | 72 |

|    | 5.11.28 SMART ENABLE OPERATIONS        | 71 |

|    | 5.11.27 SMART READ DATA                | 69 |

|    | 5.11.26 SMART                          | 69 |

|    | 5.11.25 SECURITY DISABLE PASSWORD- F6H | 66 |

|    | 5.11.24 SECURITY FREEZE LOCK- F5H      | 64 |

|    | 5.11.23 SECURITY ERASE UNIT- F4H       | 62 |

|    | 5.11.22 SECURITY ERASE PREPARE- F3H    | 60 |

|    | 5.11.21 SECURITY UNLOCK- F2H           | 58 |

|    | 5.11.20 SECURITY SET PASSWORD- F1H     | 55 |

|    | 5.11.19 Write Sector(s) – 30h          | 54 |

|    | 5.11.18 Write Multiple- C5H            | 51 |

|    | 5.11.17 WRITE DMA – CAH                | 51 |

|    | 5.11.16 Write Buffer – E8H             | 50 |

|    | 5.11.15 STANDBY IMMEDIATE –E0H         | 50 |

|    | 5.11.14 STANDBY –E2H                   | 50 |

|    | 5.11.13 SET SLEEP MODE –E6H            | 49 |

|    | 5.11.12 SET MULTIPLE MODE – C6H        |    |

|    | 5.11.11 SET FEATURES - EFH             |    |

|    | 5.11.10 READ VERIFY SECTOR(S) - 40H    |    |

|    | 5.11.9 READ SECTOR(S) - 20H            |    |

|    | 5.11.8 READ DMA - C8H                  |    |

|    | 5.11.7 Read Buffer - E4H               |    |

|    | 5.11.6 IDLE IMMEDIATE - 95H OR E1H     | 45 |

### **REVISION HISTORY**

| Revision    | <b>Description</b> Date                                    |                                    |  |  |  |  |

|-------------|------------------------------------------------------------|------------------------------------|--|--|--|--|

| Preliminary | Release First Version Dec. 2011                            |                                    |  |  |  |  |

| Rev 1.0     | Add Specification                                          | Feb. 2012                          |  |  |  |  |

| Rev. 1.1    | Modify the Access mode                                     | Modify the Access mode March. 2012 |  |  |  |  |

| Rev. 1.2    | Update performance April. 2012                             |                                    |  |  |  |  |

|             | Modify Part Number rule                                    |                                    |  |  |  |  |

| Rev. 2.0    | Update performance (TSOP:2GB-32GB; BGA:8GB-32GB) May. 2012 |                                    |  |  |  |  |

|             | Modify Part number rule                                    |                                    |  |  |  |  |

| Rev. 2.1    | Add MLC performance July.2012                              |                                    |  |  |  |  |

|             | Modify power consumption                                   |                                    |  |  |  |  |

### **List of Tables**

| TABLE 1: ICF9000 PIN ASSIGNMENTS                            | 11 |

|-------------------------------------------------------------|----|

| TABLE 2: ICF9000 PIN DESCRIPTION                            | 13 |

| Table 3: Shock/Vibration Test for iCF9000                   | 17 |

| Table 4: ICF9000 MTBF                                       | 17 |

| TABLE 5: TRUE IDE PIO MODE READ/WRITE TIMING                | 20 |

| TABLE 6: TRUE IDE MULTIWORD DMA READ/WRITE TIMING           | 21 |

| TABLE 7: TIMING DIAGRAM, ULTRA DMA MODE 0-6                 | 21 |

| TABLE 8: TRUE IDE MODE I/O FUNCTION                         | 23 |

| TABLE 9: CONFIGURATION OPTION REGISTER                      | 25 |

| TABLE 10: INFORMATION FOR CONFIGURATION OPTION REGISTER     | 25 |

| TABLE 11: PIN REPLACEMENT REGISTER                          | 25 |

| TABLE 12: INFORMATION FOR PIN REPLACEMENT REGISTER          | 25 |

| TABLE 13: SOCKET AND COPY REGISTER                          | 26 |

| TABLE 14: INFORMATION FOR SOCKET AND COPY REGISTER          | 26 |

| TABLE 15: TRUE IDE MODE I/O DECODING                        | 26 |

| Table 16: Data Register                                     | 27 |

| Table 17: Error Register                                    | 27 |

| Table 18: Feature Register                                  | 27 |

| TABLE 19: SECTOR COUNT REGISTER                             | 27 |

| TABLE 20: SECTOR NUMBER REGISTER                            | 28 |

| TABLE 21: CYLINDER LOW REGISTER                             | 28 |

| TABLE 22: CYLINDER HIGH REGISTER                            | 28 |

| Table 23: Device/Head Register                              | 28 |

| Table 24: Status Register                                   | 29 |

| TABLE 25: DEVICE CONTROL REGISTER                           | 30 |

| Table 26: Drive Address Register                            | 30 |

| TABLE 27: TIMING DIAGRAM, HARDWARE RESET                    | 31 |

| TABLE 28: TIMING DIAGRAM, POWER ON RESET                    | 31 |

| TABLE 29: IDE COMMANDS                                      | 32 |

| TABLE 30: CHECK POWER MODE INFORMATION                      | 33 |

| TABLE 31: EXECUTE DEVICE DIAGNOSTIC INFORMATION             | 33 |

| Table 32: Diagnostic                                        | 33 |

| TABLE 33: FLUSH CACHE COMMAND FOR INPUTS INFORMATION        | 34 |

| TABLE 34: FLUSH CACHE COMMAND FOR NORMAL OUTPUT INFORMATION | 34 |

| TABLE 35: FLUSH CACHE COMMAND FOR ERROR OUTPUT INFORMATION  | 35 |

| TABLE 36: IDENTIFY DEVICE INFORMATION                       | 35 |

| TABLE 37: IDENTIFY DEVICE INFORMATION                       | 36 |

| TABLE 38: IDLE INFORMATION                                  | 45 |

| TABLE 39: IDLE IMMEDIATE INFORMATION                                                    | 45 |

|-----------------------------------------------------------------------------------------|----|

| Table 40: Read buffer information                                                       | 46 |

| Table 41: Read DMA information                                                          | 46 |

| Table 42: Read sector information                                                       | 47 |

| TABLE 43: READ VERIFY SECTOR INFORMATION                                                | 47 |

| Table 44: Set feature information                                                       | 48 |

| Table 45: Feature Supported                                                             | 48 |

| TABLE 46: SET MULTIPLE MODE INFORMATION                                                 | 49 |

| TABLE 47: SET SLEEP MODE INFORMATION                                                    | 49 |

| Table 48: Standby information                                                           | 50 |

| Table 49: Standby immediate information                                                 | 50 |

| Table 50: Write buffer information                                                      | 50 |

| Table 51: Write DMA information                                                         | 51 |

| TABLE 52: WRITE MULTIPLE COMMAND FOR INPUTS INFORMATION                                 | 52 |

| TABLE 53: WRITE MULTIPLE COMMAND FOR NORMAL OUTPUT INFORMATION                          | 52 |

| TABLE 54: WRITE MULTIPLE COMMAND FOR NORMAL OUTPUT INFORMATION                          | 53 |

| Table 55: Write sector information                                                      | 54 |

| TABLE 56: SECURITY SET PASSWORD COMMAND FOR INPUTS INFORMATION                          | 55 |

| TABLE 57: SECURITY SET PASSWORD COMMAND FOR NORMAL OUTPUTS INFORMATION                  | 56 |

| TABLE 58: SECURITY SET PASSWORD COMMAND FOR ERROR OUTPUTS INFORMATION                   | 56 |

| TABLE 59: SECURITY SET PASSWORD COMMAND'S DATA CONTENT                                  | 57 |

| TABLE 60: SECURITY SET PASSWORD COMMAND'S IDENTIFIER AND SECURITY LEVEL BIT INTERACTION | 57 |

| TABLE 61: SECURITY UNLOCK COMMAND FOR INPUTS INFORMATION                                | 58 |

| TABLE 62: SECURITY UNLOCK COMMAND FOR INPUTS INFORMATION                                | 58 |

| TABLE 63: SECURITY UNLOCK COMMAND FOR INPUTS INFORMATION                                | 59 |

| Table 64: Security erase prepare command for inputs information                         | 60 |

| TABLE 65: SECURITY ERASE PREPARE COMMAND FOR NORMAL OUTPUTS INFORMATION                 | 60 |

| TABLE 66: SECURITY ERASE PREPARE COMMAND FOR ERROR OUTPUTS INFORMATION                  | 61 |

| TABLE 67: SECURITY ERASE UNIT COMMAND FOR INPUTS INFORMATION                            | 62 |

| TABLE 68: SECURITY ERASE UNIT COMMAND FOR NORMAL OUTPUTS INFORMATION                    | 62 |

| TABLE 69: SECURITY ERASE UNIT COMMAND FOR ERROR OUTPUTS INFORMATION                     | 63 |

| TABLE 70: SECURITY ERASE UNIT PASSWORD INFORMATION                                      | 64 |

| TABLE 71: SECURITY FREEZE LOCK FOR INPUTS INFORMATION                                   | 65 |

| TABLE 72: SECURITY FREEZE LOCK FOR NORMAL OUTPUTS INFORMATION                           | 65 |

| TABLE 73: SECURITY FREEZE LOCK FOR ERROR OUTPUTS INFORMATION                            | 65 |

| TABLE 74: SECURITY DISABLE PASSWORD COMMAND FOR INPUTS INFORMATION                      | 67 |

| TABLE 75: SECURITY DISABLE PASSWORD COMMAND FOR NORMAL OUTPUTS INFORMATION              | 67 |

| TABLE 76: SECURITY DISABLE PASSWORD COMMAND FOR ERROR OUTPUTS INFORMATION               | 67 |

| TABLE 77: SECURITY DISABLE PASSWORD COMMAND CONTENT                                     | 68 |

| TABLE 78: SMART FEATURE REGISTER VALUES                | 69 |

|--------------------------------------------------------|----|

| TABLE 79: SMART COMMAND FOR INPUTS INFORMATION         | 69 |

| TABLE 80: SMART COMMAND FOR NORMAL OUTPUTS INFORMATION | 69 |

| TABLE 81: SMART DATA STRUCTURE                         | 70 |

| TABLE 82: SMART ENABLE COMMAND FOR INPUTS INFORMATION  | 71 |

| TABLE 83: SMART COMMAND FOR NORMAL OUTPUTS INFORMATION | 71 |

| TABLE 84: SMART DISABLE COMMAND FOR INPUTS INFORMATION | 72 |

| TABLE 85: SMART COMMAND FOR NORMAL OUTPUTS INFORMATION | 72 |

| TARLE 86: DEVICE PARAMETER                             | 73 |

# **List of Figures**

| FIGURE 1: MECHANICAL DIMENSION OF ICF9000               | 18 |

|---------------------------------------------------------|----|

| FIGURE 2: READ/WRITE TIMING DIAGRAM, PIO MODE           | 19 |

| FIGURE 3: TRUE IDE MULTIWORD DMA MODE READ/WRITE TIMING | 20 |

| FIGURE 4: TIMING DIAGRAM POWER ON PEGET                 | 21 |

### 1. Introduction

The InnoDisk Industrial CompactFlash® 9000 Memory Card (iCF9000) products provide high capacity solid-state flash memory that electrically complies with the True IDE Mode that is electrically compatible with an IDE disk drive. The original CF form factor card can be used in any system that has a CF slot. Designed to replace traditional rotating disk drives, InnoDisk Industrial CompactFlash® 9000 Memory Cards are embedded solid-state data storage systems for mobile computing and the industrial work place. The Industrial CompactFlash® features an extremely lightweight, reliable, low-profile form factor. Industrial CompactFlash® 9000 (iCF9000) support advanced PIO (0-6), Multiword DMA (0-4), Ultra DMA (0-7) transfer mode, multi-sector transfers, and LBA addressing.

### 2. Features

The Industrial ATA products provide the following system features:

- Capacities: 2GB/4GB/8GB/16GB/32GB

- Fully compatible with CompactFlash<sup>®</sup> specification version 6.0

- Fully compatible with PC Card Standard.

- · Fully compatible with the IDE standard interface, ATA Standard

- · Three access modes

- True IDE Mode

- PC Card Memory Mode

- PC Card I/O Mode

- ECC (Error Correction Code) function: 72 bits/ per 1 Kbyte

- +3.3V/+5V single power supply operation

- Support Auto Stand-by and Sleep Mode.

- Power Consumption

- Quad:

Active mode

9

Read operation: 210 mA(max.)

Write operation: 210 mA(max.)

Power Down mode: 150 mA(max.)

- Support transfer modes: PIO(0-6), Multiword DMA (0-4) and Ultra DMA(0-7)

- MTBF 3,000,000 hours

• R/W performance(Quad):

| Flash type | Flash Package | Capacity | Max. Read (MB/s) | Max. Write (MB/s) |  |

|------------|---------------|----------|------------------|-------------------|--|

|            |               | 2GB      | 80               | 70                |  |

|            |               | 4GB      | 80               | 70                |  |

|            | TSOP          | 8GB      | 80               | 70                |  |

| SLC        |               | 16GB     | 100              | 95                |  |

| SLO        |               | 32GB     | 100              | 95                |  |

|            | BGA           | 8GB      | 115              | 70                |  |

|            |               | 16GB     | 115              | 100               |  |

|            |               | 32GB     | 115              | 100               |  |

| MLC        | TSOP          | 16GB     | 90               | 20                |  |

| 20         |               | 32GB     | 50               | 20                |  |

- Operating temperature range:

Standard Grade: 0°C ~ +70°C

Industrial Grade: -40°C ~ +85°C

• Storage temperature range: -55°C ~ +95°C

## 3. Pin Assignment

See Table 1 for Icf9000 pin assignments.

Table 1: Icf9000 Pin Assignments

|            | True IDE Mode    |     |            |                     |     |  |  |

|------------|------------------|-----|------------|---------------------|-----|--|--|

| Pin<br>No. | Name             | I/O | Pin<br>No. | Name                | I/O |  |  |

| 1          | GND              |     | 29         | D13 <sup>1</sup>    | I/O |  |  |

| 2          | D03              | I/O | 30         | D14 <sup>1</sup>    | I/O |  |  |

| 3          | D04              | I/O | 31         | D15 <sup>1</sup>    | I/O |  |  |

| 4          | D05              | I/O | 32         | -CS1 <sup>1</sup>   | 1   |  |  |

| 5          | D06              | I/O | 33         | -VS1                | GND |  |  |

| 6          | D07              | I/O |            |                     |     |  |  |

| 7          | -CS0             | I   | 34         | -IORD <sup>7</sup>  | I   |  |  |

| 8          | A10 <sup>2</sup> | GND |            |                     |     |  |  |

| 9          | -ATA SEL         | GND | 25         | -IOWR <sup>7</sup>  | ı   |  |  |

| 10         | A09 <sup>2</sup> | GND | 35         | -IOWK               | '   |  |  |

| 11         | A08 <sup>2</sup> | GND | 36         | -WE <sup>3</sup>    | I   |  |  |

| 12         | A07 <sup>2</sup> | GND | 37         | INTRQ               | 0   |  |  |

| 13         | VCC              | GND | 38         | VCC                 |     |  |  |

| 14         | A06 <sup>2</sup> | GND | 39         | -CSEL               | I   |  |  |

| 15         | A05 <sup>2</sup> | GND | 40         | -VS2                | NC  |  |  |

| 16         | A04 <sup>2</sup> | GND | 41         | -RESET              | I   |  |  |

| 17         | A03 <sup>2</sup> | GND |            |                     |     |  |  |

| 18         | A02              | 1   | 42         | IORDY <sup>1</sup>  | 0   |  |  |

| 19         | A01              | I   |            |                     |     |  |  |

| 20         | A00              | 1   | 43         | DMARQ               | 0   |  |  |

| 21         | D00              | I/O | 44         | -DMACK <sup>6</sup> | I   |  |  |

| 22         | D01              | I/O | 45         | -DASP               | I/O |  |  |

| 23         | D02              | I/O | 46         | -PDIAG              | I/O |  |  |

| 24         | -IOCS16          | NC  | 47         | D08 <sup>1</sup>    | I/O |  |  |

| 25         | -CD2             | GND | 48         | D09 <sup>1</sup>    | I/O |  |  |

| 26         | -CD1             | GND | 49         | D10 <sup>1</sup>    | I/O |  |  |

| 27         | D11 <sup>1</sup> | I/O | 50         | GND                 |     |  |  |

| 28         | D12 <sup>1</sup> | I/O |            |                     |     |  |  |

### Note:

- These signals are required only for 16 bit accesses and not required when installed in 8 bit systems. Devices should allow for 1-state signals not to consume current.

- 2) The signal should be grounded by the host.

- 3) The signal should be tied to VCC by the host.

- 4) The mode is optional for CF+ Cards, but required for CompactFlash® Storage Cards.

- The -CSEL signal is ignored by the card in PC Card modes. However, because it is not pulled up on the card in these modes, it should not be left floating by the host in PC Card modes. In these modes, the pin should be connected by the host to PC Card A25 or grounded by the host.

- 6) If DMA operations are not used, the signal should be held high or tied to VCC by the host. For proper operation in older hosts: while DMA operations are not active, the card shall ignore this signal, including a floating condition

- 7) Signal usage in True IDE Mode except when Ultra DMA mode protocol is active.

- 8) Signal usage in True IDE Mode when Ultra DMA mode protocol DMA Write is active.

- 9) Signal usage in True IDE Mode when Ultra DMA mode protocol DMA Read is active.

# 4. Pin Description

13

Table 2 describes the pin descriptions for Icf9000

Table 2: Icf9000 Pin Description

| Pin No.                                                | Pin Name   | I/O | Mode                                                                                                 | Description                                                                                                                                                                                                                                                                           |

|--------------------------------------------------------|------------|-----|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18,19,20                                               | A2 – A0    | I   | True IDE<br>Mode                                                                                     | In True IDE Mode, only A[2:0] are used to select the one of eight registers in the Task File, the remaining address lines should be grounded by the host.                                                                                                                             |

| 46                                                     | -PDIAG     | I/O | True IDE Mode, this input / output is the F Diagnostic signal in the Master / Slave handsh protocol. |                                                                                                                                                                                                                                                                                       |

| 45                                                     | -DASP      | I/O | True IDE<br>Mode                                                                                     | In the True IDE Mode, this input/output is the Disk Active/Slave Present signal in the Master/Slave handshake protocol.                                                                                                                                                               |

| 26, 25                                                 | -CD1, -CD2 | 0   | True IDE<br>Mode                                                                                     | This signal is the same for all modes.                                                                                                                                                                                                                                                |

| 7, 32                                                  | -CS0, -CS1 | I   | True IDE<br>Mode                                                                                     | In the True IDE Mode, -CS0 is the chip select for the task file registers while -CS1 is used to select the Alternate Status Register and the Device Control Register.  While –DMACK is asserted, -CS0 and –CS1 shall be held negated and the width of the transfers shall be 16 bits. |

| 39                                                     | -CSEL      | I   | True IDE<br>Mode                                                                                     | This internally pulled up signal is used to configure this device as a Master or a Slave when configured in the True IDE Mode. When this pin is grounded, this device is configured as a Master. When the pin is open, this device is configured as a Slave.                          |

| 2,3,4,5,6<br>31,30,29<br>28,27,49<br>48,47,23<br>22,21 | D15 - D00  | I/O | True IDE<br>Mode                                                                                     | In True IDE Mode, all Task File operations occur in byte mode on the low order bus D[7:0] while all data transfers are 16 bit using D[15:0].                                                                                                                                          |

| 1, 50                                                  | GND        | -   | True IDE<br>Mode                                                                                     | This signal is the same for all modes.                                                                                                                                                                                                                                                |

| 43 | DMARQ    | 0 | True IDE<br>Mode | This signal is a DMA Request that is used for DMA data transfers between host and device. It shall be asserted by the device when it is ready to transfer data to or from the host. For Multiword DMA transfers, the direction of data transfer is controlled by -IORD and -IOWR. This signal is used in a handshake manner with -DMACK, i.e., the device shall wait until the host asserts -DMACK before negating DMARQ, and reasserting DMARQ if there is more data to transfer. DMARQ shall not be driven when the device is not selected. While a DMA operation is in progress, -CS0 and -CS1 shall be held negated and the width of the transfers shall be 16 bits. If there is no hardware support for DMA mode in the host, this output signal is not used and should not be connected at the host. In this case, the BIOS must report that DMA mode is not supported by the host so that device drivers will not attempt DMA mode. |

|----|----------|---|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | -IORD    |   | True IDE<br>Mode | In True IDE Mode, while Ultra DMA mode is not active, this signal has the same function as in PC Card I/O Mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 34 | -HDMARDY | - |                  | In True IDE Mode when Ultra DMA mode DMA Read is active, this signal is asserted by the host to indicate that the host is read to receive Ultra DMA data-in bursts. The host may negate -HDMARDY to pause an Ultra DMA transfer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|    | HSTROBE  |   |                  | In True IDE Mode when Ultra DMA mode DMA Write is active, this signal is the data out strobe generated by the host. Both the rising and falling edge of HSTROBE cause data to be latched by the device. The host may stop generating HSTROBE edges to pause an Ultra DMA data-out burst.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 35 | -IOWR    | I | True IDE<br>Mode | In True IDE Mode, while Ultra DMA mode protocol is not active, this signal has the same function as in PC Card I/O Mode. When Ultra DMA mode protocol is supported, this signal must be negated before entering Ultra DMA mode protocol.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|    | STOP     |   |                  | In True IDE Mode, while Ultra DMA mode protocol is active, the assertion of this signal causes the termination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|        |            |   |                  | of the Ultra DMA burst.                                                                                                                                                                                                                                                                                                                                        |

|--------|------------|---|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9      | -ATA SEL   | I | True IDE<br>Mode | To enable True IDE Mode this input should be grounded by the host.                                                                                                                                                                                                                                                                                             |

| 37     | INTRQ      | О | True IDE<br>Mode | In True IDE Mode signal is the active high Interrupt Request to the host.                                                                                                                                                                                                                                                                                      |

| 44     | -DMACK     | I | True IDE<br>Mode | This is a DMA Acknowledge signal that is asserted by the host in response to DMARQ to initiate DMA transfers. While DMA operations are not active, the card shall ignore the -DMACK signal, including a floating condition. If DMA operation is not supported by a True IDE Mode only host, this signal should be driven high or connected to VCC by the host. |

| 41     | -RESET     | I | True IDE<br>Mode | In the True IDE Mode, this input pin is the active low hardware reset from the host.                                                                                                                                                                                                                                                                           |

| 13, 38 | VCC        | - | True IDE<br>Mode | This signal is the same for all modes.                                                                                                                                                                                                                                                                                                                         |

| 33, 40 | -VS1, -VS2 | 0 | True IDE<br>Mode | This signal is the same for all modes.                                                                                                                                                                                                                                                                                                                         |

|        | IORDY      |   |                  | In True IDE Mode, except in Ultra DMA modes, this output signal may be used as IORDY.                                                                                                                                                                                                                                                                          |

| 42     | -DDMARDY   | 0 | True IDE         | In True IDE Mode, when Ultra DMA mode DMA Write is active, this signal is asserted by the host to indicate that the device is read to receive Ultra DMA data-in bursts. The device may negate -DDMARDY to pause an Ultra DMA transfer.                                                                                                                         |

|        |            |   |                  | In True IDE Mode, when Ultra DMA mode DMA Write is active, this signal is the data out strobe generated by the device. Both the rising and falling edge of DSTROBE cause data to be latched by the host. The device may stop generating DSTROBE edges to pause an Ultra DMA data-out burst.                                                                    |

| 36     | -WE        | 1 | True IDE<br>Mode | In True IDE Mode, this input signal is not used and should be connected to VCC by the host.                                                                                                                                                                                                                                                                    |

| 24 | -IOCS16 | 0 |      | In True IDE Mode this output signal is asserted low when |

|----|---------|---|------|----------------------------------------------------------|

|    |         |   | Mode | this device is expecting a word data transfer cycle.     |

16 Rev 2.1 Datasheet, July. 2012

### 5. Specifications

### 5.1 CE and FCC Compatibility

Icf9000 conforms to CE and FCC requirements.

### 5.2 RoHS Compliance

Icf9000 is fully compliant with RoHS directive.

### 5.3 Environmental Specifications

### 5.3.1 Temperature Ranges

Operating Temperature Range:

- Standard Grade: 0°C to +70°C

- Industrial Grade: -40°C to +85°C

Storage Temperature Range: -55°C to +95°C

### 5.3.2 Humidity

17

Relative Humidity: 10-95%, non-condensing

### 5.3.3 Shock and Vibration

Table 3: Shock/Vibration Test for Icf9000

| Reliability      | Test Conditions                | Reference Standards |

|------------------|--------------------------------|---------------------|

| Vibration        | 7 Hz to 2 KHz, 20G, 3 axes     | IEC 68-2-6          |

| Mechanical Shock | Duration: 0.5ms, 1500G, 3 axes | IEC 68-2-27         |

### 5.3.4 Mean Time between Failures (MTBF)

Table 4 summarizes the MTBF prediction results for various Icf9000 configurations. The analysis was performed using a RAM Commander<sup>™</sup> failure rate prediction.

- Failure Rate: The total number of failures within an item population, divided by the total number of life units expended by that population, during a particular measurement interval under stated condition.

- Mean Time between Failures (MTBF): A basic measure of reliability for repairable items:

The mean number of life units during which all parts of the item perform within their specified limits, during a particular measurement interval under stated conditions.

Table 4: Icf9000 MTBF

| Product | Condition                 | MTBF (Hours) |

|---------|---------------------------|--------------|

| Icf9000 | Telcordia SR-332 GB, 25°C | 3,000,000    |

### 5.4 Mechanical Dimensions

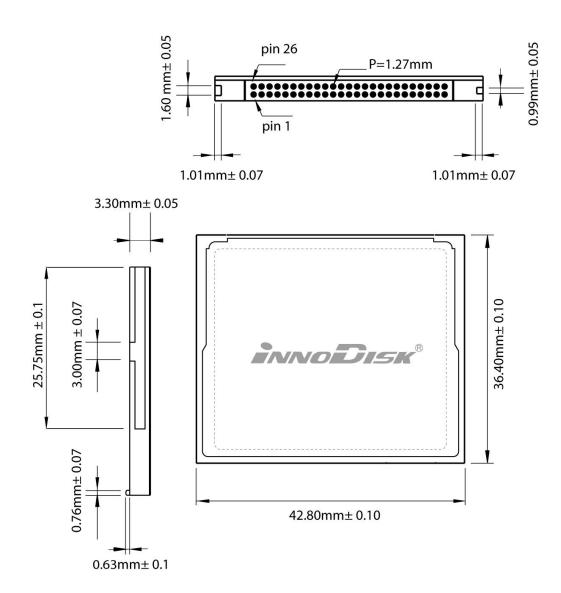

Mechanical Dimension: 42.80±0.1/36.40±0.1/3.30±0.05mm (W/T/H)

Figure 1: Mechanical Dimension of Icf9000

### 5.5 Electrical Specifications

### 5.5.1 DC Characteristic

Power supply requirement: 5V±0.5V DC or 3.3±0.3V

### 5.5.2 Timing Specifications

### 5.5.2.1 True IDE PIO Mode Read/Write Timing Specification

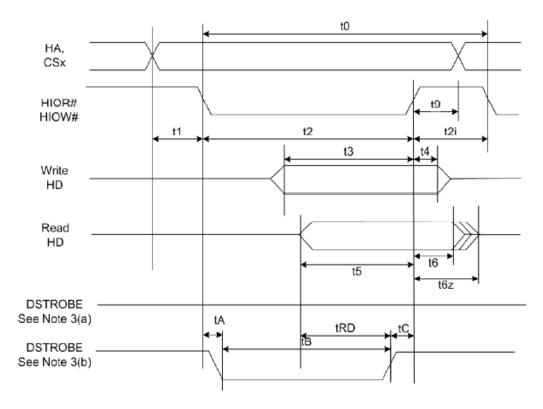

Figure 2: Read/Write Timing Diagram, PIO Mode

### Note:

- 1. Device address comprises CS1#, CS0#, and HA[2:0].

- 2. Data comprises HD[15:0] (16-bit) or HD[7:0] (8-bit).

- 3. The negation of DSTROBE by the device is used to lengthen the PIO cycle. Whether the cycle is to be extended is determined by the host after Ta from the assertion of HIOR# or HIOW#. The assertion and negation of DSTROBE is described in the following three cases. (a) The device never negates DSTROBE: No wait is generated. (b) Device drives DSTROBE low before Ta: a wait is generated. The cycle is completed after DSTROBE is reasserted. For cycles in which a wait is generated and HIOR# is asserted, the device places read data on D15-D00 for Trd before DSTROBE is asserted.

IORDY assertion to release (max.)

|                       | Table 5: True ID                         | E PIO MOG | e Read/with | te riming |        |        |

|-----------------------|------------------------------------------|-----------|-------------|-----------|--------|--------|

| PIO                   | timing parameters                        | Mode 0    | Mode 1      | Mode 2    | Mode 3 | Mode 4 |

| t <sub>o</sub>        | Cycle time (min.)                        | 600       | 383         | 240       | 180    | 120    |

| t <sub>1</sub>        | Address valid to HIOR-/HIOW-setup (min.) | 70        | 50          | 30        | 30     | 25     |

| t <sub>2</sub>        | HIOR-/HIOW- 16-bit (min.)                | 165       | 125         | 100       | 80     | 70     |

| t <sub>2</sub>        | HIOR-/HIOW- Register 8-bit (min.)        | 290       | 290         | 290       | 80     | 70     |

| t <sub>2i</sub>       | HIOR-/HIOW- recovery time (min.)         | -         | -           | -         | 70     | 25     |

| t <sub>3</sub>        | HIOW- data setup (min.)                  | 60        | 45          | 30        | 30     | 20     |

| t <sub>4</sub>        | HIOW- data hold (min.)                   | 30        | 20          | 15        | 10     | 10     |

| <b>t</b> <sub>5</sub> | HIOR- data setup (min.)                  | 50        | 35          | 20        | 20     | 20     |

| t <sub>6</sub>        | HIOR- data hold (min.)                   | 5         | 5           | 5         | 5      | 5      |

| t <sub>6z</sub>       | HIOR- data tri-state (max.)              | 30        | 30          | 30        | 30     | 30     |

| t <sub>9</sub>        | HIOR-/HIOW- to address valid hold        | 20        | 15          | 10        | 10     | 10     |

| t <sub>RD</sub>       | Read data valid to IORDY active (min.)   | 0         | 0           | 0         | 0      | 0      |

| t <sub>A</sub>        | IORDY setup time                         | 35        | 35          | 35        | 35     | 35     |

| t <sub>B</sub>        | IORDY pulse width (max.)                 | 1250      | 1250        | 1250      | 1250   | 1250   |

Table 5: True IDE PIO Mode Read/Write Timing

### 5.5.2.2 True IDE Multiword DMA Mode Read/Write Timing Specification

5

5

5

5

5

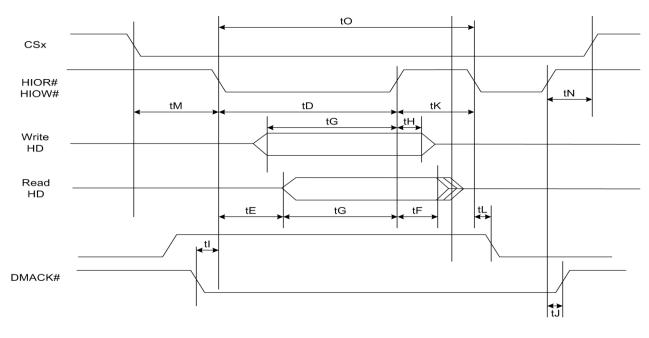

Figure 3: True IDE Multiword DMA Mode Read/Write Timing

### Note:

- 1. If a card cannot sustain continuous, minimum cycle time DMA transfers, it may negate DMARQ during the time from the start of a DMA transfer cycle (to suspend DMA transfers in progress) and reassertion of the signal at a relatively later time to continue DMA transfer operations.

- 2. The host may negate this signal to suspend the DMA transfer in progress.

Table 6: True IDE Multiword DMA Read/Write Timing

| Multi           | word DMA timing parameters         | Mode 0 | Mode 1 | Mode 2 |

|-----------------|------------------------------------|--------|--------|--------|

| t <sub>o</sub>  | Cycle time (min.)                  | 480    | 150    | 120    |

| $t_D$           | HIOR-/HIOW- assertion width (min.) | 215    | 80     | 70     |

| t <sub>E</sub>  | HIOR- data access (max.)           | 150    | 60     | 50     |

| t <sub>F</sub>  | HIOR- data hold (min.)             | 5      | 5      | 5      |

| t <sub>G</sub>  | HIOR-/HIOW- data setup (min.)      | 100    | 30     | 20     |

| t <sub>H</sub>  | HIOW- data hold (min.)             | 20     | 15     | 10     |

| tı              | DMACK to HIOR-/HIOW- setup (min.)  | 0      | 0      | 0      |

| tJ              | HIOR-/HIOW- to DMACK hold (min.)   | 20     | 5      | 5      |

| t <sub>KR</sub> | HIOR- negated width (min.)         | 50     | 50     | 25     |

| t <sub>KW</sub> | HIOW- negated width (min.)         | 215    | 50     | 25     |

| $t_{LR}$        | HIOR- to DMARQ delay (max.)        | 120    | 40     | 35     |

| t <sub>LW</sub> | HIOW- to DMARQ delay (max.)        | 40     | 40     | 35     |

| t <sub>M</sub>  | CS1-, CS0- valid to HIOR-/HIOW-    | 50     | 30     | 25     |

| t <sub>N</sub>  | CS1-, CS0- hold                    | 15     | 10     | 10     |

### 5.5.2.3 True IDE Ultra DMA Mode Data Burst Timing Specification

Table 7: Timing Diagram, Ultra DMA Mode 0-6

| Ultra             | DMA                                         | timing                        | Mode | 0    | Mode | 1    | Mode | 2    | Mode | 3    | Mode | 4    | Mode | 5    | Mode | 6    |

|-------------------|---------------------------------------------|-------------------------------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|

| para              | parameters                                  |                               | Min. | Max. | Min. | Max. | Min. | Min. | Max. | Min. | Max. | Max. | Max. | Min. | Max. | Max. |

| t <sub>2CYC</sub> | Typical average two c                       | sustained                     | 240  | -    | 160  | -    | 90   | -    | 60   | -    | 60   | -    | 40   | -    | 30   | -    |

| t <sub>cyc</sub>  | variations                                  | and clock<br>(from<br>edge to | 112  | -    | 73   | -    | 39   | -    | 25   | -    | 25   | -    | 16.8 | -    | 13   | -    |

| t <sub>2CYC</sub> | Two cycle time for clock variations edge to | ations (from                  | 230  | -    | 153  | -    | 86   | -    | 57   | -    | 57   | -    | 38   | -    | 29   | -    |

|                  | edge or from falling edge                                                                      |     |     |     |     |     |     |     |     |     |     |     |    |     |    |

|------------------|------------------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|----|-----|----|

|                  | to next falling edge of                                                                        |     |     |     |     |     |     |     |     |     |     |     |    |     |    |

|                  | STROBE)                                                                                        |     |     |     |     |     |     |     |     |     |     |     |    |     |    |

| t <sub>DS</sub>  | Data setup time (at recipient)                                                                 | 15  | -   | 10  | -   | 7   | -   | 5   | -   | 5   | -   | 4   | -  | 2.6 | -  |

| t <sub>DH</sub>  | Data hold time (at recipient)                                                                  | 5   | -   | 5   | -   | 5   | -   | 5   | -   | 5   | -   | 4.6 | -  | 3.5 | -  |

| t <sub>DVS</sub> | Data valid setup time at sender (from data bus being valid until STROBE edge)                  | 70  | -   | 48  | -   | 20  | -   | 6.7 | -   | 6.7 | -   | 4.8 | -  | 4   | -  |

| t <sub>DVH</sub> | Data valid hold time at sender (from STROBE edge until data may become invalid)                | 6.2 | -   | 6.2 | -   | 6.2 | -   | 6.2 | -   | 6.2 | -   | 4.8 | -  | 4   | -  |

| t <sub>LI</sub>  | Limited interlock time                                                                         | 0   | 150 | 0   | 150 | 0   | 100 | 0   | 100 | 0   | 100 | 0   | 75 | 0   | 60 |

| t <sub>MLI</sub> | Interlock time with minimum                                                                    | 20  | -   | 20  | -   | 20  | -   | 20  | -   | 20  | -   | 20  | -  | 20  | -  |

| t <sub>UI</sub>  | Unlimited interlock time                                                                       | 0   | -   | 0   | -   | 0   | -   | 0   | -   | 0   | -   | 0   | -  | 0   | -  |

| t <sub>AZ</sub>  | Maximum time allowed for output drivers to release (from being asserted or negated)            | -   | 10  | -   | 10  | -   | 10  | -   | 10  | -   | 10  | -   | 10 | -   | 10 |

| t <sub>ZAH</sub> | Minimum delay time                                                                             | 20  | -   | 20  | -   | 20  | -   | 20  | -   | 20  | -   | 20  | -  | 20  | -  |

| t <sub>ZAD</sub> | required for output<br>drivers to assert or<br>negate (from released<br>state)                 | 0   | -   | 0   | -   | 0   | -   | 0   | -   | 0   | -   | 0   | -  | 0   | -  |

| t <sub>ENV</sub> | Envelope time (from DMACK- to STOP and HDMARDY- during data out burst initiation)              | 20  | 70  | 20  | 70  | 20  | 55  | 20  | 55  | 20  | 55  | 20  | 50 | 20  | 50 |

| t <sub>RFS</sub> | Ready-to-final-STROBE time (no STROBE edges shall be sent this long after negation of DMARDY-) | -   | 75  | -   | 70  | -   | 60  | -   | 60  | -   | 60  | -   | 50 | -   | 50 |

| t <sub>RP</sub>   | Ready-to-pause time (time that recipient shall wait to initiate pause after negating DMARDY-)    | 160 | -   | 125 | -   | 100 | -   | 100 | -   | 100 | -   | 85 | -  | 85 | -  |

|-------------------|--------------------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|----|----|----|----|

| t <sub>IORD</sub> | Pull-up time before allowing IORDY to be released                                                | -   | 20  | -   | 20  | -   | 20  | -   | 20  | -   | 20  | -  | 20 | -  | 20 |

| t <sub>ZIOR</sub> | Minimum time device<br>shall wait before driving<br>IORDY                                        | 0   | -   | 0   | -   | 0   | -   | 0   | -   | 0   | -   | 0  | -  | 0  | -  |

| t <sub>ACK</sub>  | Setup and hold times for DMACK- (before assertion or negation)                                   | 20  | -   | 20  | -   | 20  | -   | 20  | -   | 20  | -   | 20 | -  | 20 | -  |

| t <sub>SS</sub>   | Time from STROBE edge to negation of DMARQ or assertion of STOP (when sender terminates a burst) | 50  |     | 50  | -   | 50  | -   | 50  | -   | 50  | -   | 50 | -  | 50 | -  |

| t <sub>FS</sub>   | First STROBE time (for device to first negate DSTROBE from STOP during a data in burst)          | -   | 230 | -   | 200 | -   | 130 | -   | 120 | -   | 120 | -  | 90 | -  | 80 |

### **5.6 Transfer Function**

23

### 5.6.1 True IDE Mode I/O Transfer Function

The Icf9000 can be configured in a True IDE Mode of operation. The Icf9000 is configured in this mode only when –OE input signal is grounded by the host during the power off to power on cycle.

**Table 8: True IDE Mode I/O Function**

| Function Code | -CS1 | -CS0 | -A0~A2 | -DMACK | -IORD | -IOWR | D15~D8    | D7~D0     |

|---------------|------|------|--------|--------|-------|-------|-----------|-----------|

|               | L    | L    | Х      | Х      | Х     | Х     | Undefined | Undefined |

|               |      |      |        |        |       |       | In/Out    | In/Out    |

| Invalid Mode  | L    | Х    | Х      | L      | L     | Х     | Undefined | Undefined |

| invalid Mode  |      |      |        |        |       |       | Out       | Out       |

|               | L    | Х    | Х      | L      | Х     | L     | Undefined | Undefined |

|               |      |      |        |        |       |       | In        | In        |

|                   | Х | L | Х    | L | L        | Х | Undefined  | Undefined  |

|-------------------|---|---|------|---|----------|---|------------|------------|

|                   |   |   |      |   |          |   | Out        | Out        |

|                   | Х | L | Х    | L | Х        | L | Undefined  | Undefined  |

|                   |   |   |      |   |          |   | In         | In         |

| Standby Mode      | Н | Н | Х    | Н | Х        | Х | High Z     | High Z     |

| Task File Write   | Н | L | 1-7h | Н | Н        | L | Don't Care | Data In    |

| Task File Read    | Н | L | 1-7h | Н | L        | Н | High Z     | Data In    |

| PIO Data Register | Н | L | 0    | Н | Н        | L | Odd-Byte   | Even-Byte  |

| Write             |   |   |      |   |          |   | In         | In         |

| DMA Data Register | Н | Н | Х    | L | Н        | L | Odd-Byte   | Even-Byte  |

| Write             |   |   |      |   |          |   | In         | In         |

| Ultra DMA Data    | Н | Н | Х    | L | See Note | 1 | Odd-Byte   | Even-Byte  |

| Register Write    |   |   |      |   |          |   | In         | In         |

| PIO Data Register | Н | L | 0    | Н | L        | Н | Odd-Byte   | Even-Byte  |

| Read              |   |   |      |   |          |   | Out        | Out        |

| DMA Data Register | Н | Н | Х    | L | L        | Н | Odd-Byte   | Even-Byte  |

| Read              |   |   |      |   |          |   | Out        | Out        |

| Ultra DMA Data    | Н | Н | Х    | L | See Note | 2 | Odd-Byte   | Even-Byte  |

| Register Read     |   |   |      |   |          |   | Out        | Out        |

| Control Register  | L | Н | 6h   | Н | Н        | L | Don't Care | Control In |

| Write             |   |   |      |   |          |   |            |            |

| Alt Status Read   | L | Н | 6h   | Н | L        | Н | High Z     | Status Out |

| Drive Address     | L | Н | 7h   | Н | L        | Н | High Z     | Data Out   |

Note1: In Ultra DMA Data Register Write mode the signals –IORD, -IOWR and IORDY are redefined and used as follows: -IORD as HSTROBE, -IOWR as STOP and IORDY as –DDMARDY. Data transfers with each edge of HSTROBE.

Note2: In Ultra DMA Data Register Read mode the signals –IORD, -IOWR and IORDY are redefined and used as follows: -IORD as –HDMARDY H, -IOWR as STOP and IORDY as DSTROBE. Data transfer with each edge of DSTROBE.

### 5.7 Configuration Register

24

### 5.7.1 Configuration Option Register (200h in Attribute Memory)

The Configuration Option Register is used to configure the cards interface, address decoding and interrupt and to issue a soft reset to the Icf9000.

**Table 9: Configuration Option Register**

| Operation | D7     | D6       | D5    | D4    | D3    | D2    | D1    | D0    |

|-----------|--------|----------|-------|-------|-------|-------|-------|-------|

| R/W       | SRESET | LevelREQ | Conf5 | Conf4 | Conf3 | Conf2 | Conf1 | Conf0 |

Table 10: Information for Configuration Option Register

| Name     | Description                                                                                 |  |  |  |  |  |  |  |  |

|----------|---------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| SRSET    | Soft Reset: Setting this bit to one (1), waiting the minimum reset time and returning to    |  |  |  |  |  |  |  |  |

|          | zero(0) places the Icf9000 in the reset state. Setting this bit to one (1) is equivalent to |  |  |  |  |  |  |  |  |

|          | assertion of the +RESET signal except that the SRESET bit is not cleared. Returning         |  |  |  |  |  |  |  |  |

|          | this bit to zero (0) leaves the lcf9000 in the same un-configured, Reset state as           |  |  |  |  |  |  |  |  |

|          | following power-up and hardware reset. Contrast with Soft Reset in the Device Control       |  |  |  |  |  |  |  |  |

|          | Register.                                                                                   |  |  |  |  |  |  |  |  |

| LevelREQ | This bit is set to one (1) then Level Mode Interrupt is selected, and zero (0) then Pulse   |  |  |  |  |  |  |  |  |

|          | Mode is selected. Set to zero (0) by Reset.                                                 |  |  |  |  |  |  |  |  |

| Conf5-0  | Configuration Index: Set to zero (0) by reset. It is used to select operation mode of the   |  |  |  |  |  |  |  |  |

|          | Icf9000 as shown below                                                                      |  |  |  |  |  |  |  |  |

Note: Conf5 and Conf4 are reserved for CompactFlash Storage cards and shall be written as zero(0).

### 5.7.2 Pin Replacement register (204h in Attribute Memory)

Table 11: Pin Replacement Register

| Operation | D7 | D6 | D5     | D4 | D3 | D2 | D1     | D0 |

|-----------|----|----|--------|----|----|----|--------|----|

| Read      | 0  | 0  | Cready | 0  | 1  | 1  | Rready | 0  |

| Write     | 0  | 0  | Cready | 0  | 0  | 0  | Mready | 0  |

**Table 12: Information for Pin Replacement Register**

| Name   | Description                                                                     |

|--------|---------------------------------------------------------------------------------|

| Cready | This bit is set to one (1) when the bit Rready changes state. This bit can also |

|        | be written by the host.                                                         |

| Rready | This bit is used to determine the internal state of the READY signal. This bit  |

|        | may be used to determine the state of the READY signal as this pin has been     |

|        | reallocated for use as Interrupt Request on an I/O card. When written, this bit |

|        | acts as a mask (Mready) for writing the corresponding bit Cready.               |

| Mready | This bit acts as a mask for writing corresponding bit Cready.                   |

### 5.7.3 Socket and Copy Register (206h in Attribute Memory)

This register contains additional configuration information. This register is always written by the system before writing the card's Configuration Index Register. This register is used for identification of the card from the other card.

25 Rev 2.1 Datasheet, July. 2012

**Table 13: Socket and Copy Register**

| Operation | D7 | D6 | D5 | D4        | D3 | D2 | D1 | D0 |

|-----------|----|----|----|-----------|----|----|----|----|

| Read      | 0  | 0  | 0  | Obsolete  | 0  | 0  | 0  | 0  |

|           |    |    |    | (Drive #) |    |    |    |    |

| Write     | 0  | 0  | 0  | Obsolete  | Х  | Х  | Х  | Х  |

|           |    |    |    | (Drive #) |    |    |    |    |

Table 14: Information for Socket and Copy Register

| Name              | Description                                      |

|-------------------|--------------------------------------------------|

| Obsolete(Drive #) | This bit is obsolete and should be written as 0. |

### 5.8 Software Interface

### 5.8.1 True IDE Mode Addressing

When the Icf9000 is configured in the True IDE mode, the I/O decoding is as follows:

Table 15: True IDE Mode I/O Decoding

| -CS1 | -CS0 | A2 | A1 | A0 | -DMACK | -IORD=0          | -IOWR=0          | Note    |

|------|------|----|----|----|--------|------------------|------------------|---------|

| 1    | 0    | 0  | 0  | 0  | 1      | PIO RD Data      | PIO WR Data      | 8 or 16 |

|      |      |    |    |    |        |                  |                  | bit     |

| 1    | 1    | Χ  | Х  | Χ  | 0      | DMA RD Data      | DMA WR Data      | 16 bit  |

| 1    | 0    | 0  | 0  | 1  | 1      | Error Register   | Features         | 8 bit   |

| 1    | 0    | 0  | 1  | 0  | 1      | Sector Count     | Sector Count     | 8 bit   |

| 1    | 0    | 0  | 1  | 1  | 1      | Sector No.       | Sector No.       | 8 bit   |

| 1    | 0    | 1  | 0  | 0  | 1      | Cylinder Low     | Cylinder Low     | 8 bit   |

| 1    | 0    | 1  | 0  | 1  | 1      | Cylinder High    | Cylinder High    | 8 bit   |

| 1    | 0    | 1  | 1  | 0  | 1      | Select Card/Head | Select Card/Head | 8 bit   |

| 1    | 1    | 1  | 1  | 1  | 1      | Status           | Command          | 8 bit   |

| 0    | 1    | 1  | 1  | 0  | 1      | Alt Status       | Device Control   | 8 bit   |

### 5.8.2 CF-ATA Register

The following section describes the hardware registers used by the host software to issue commands to the lcf9000.

### Note:

In True IDE Mode of operation, the size of the transfer is based solely on the register being addressed.

All registers are 8 bit only except for the Data Register, which is normally 16 bits, but can be

programmed to use 8 bit transfers for Non-DMA operations through the use of the Set Features command. The data register is also 8 bits during a portion of the Read Long and Write Long commands, which exist solely for historical reasons and should not be used.

### 5.8.2.1 Data Register

The Data Register is a 16 bit register, and it is used to transfer data blocks between the card and the host. This register overlaps the Error Register. This register can be accessed in word and byte mode.

Table 16: Data Register

| Data F | Registe | •   |     |     |     |    |    |    |    |    |    |    |    |    |    |

|--------|---------|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|

| D15    | D14     | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

### 5.8.2.2 Error Register

This register contains additional information about the source of an error when an error is indicated in bit 0 of the Status register. The bits are defined as follows.

Table 17: Error Register

| BBK | UNC | 0  | IDNF | 0  | ABRT | 0  | AMNF |

|-----|-----|----|------|----|------|----|------|

| D7  | D6  | D5 | D4   | D3 | D2   | D1 | D0   |

### 5.8.2.3 Feature Register

This register provides information regarding features of the card that the host can utilize. This register is also accessed in PC Card modes on data D15-D8 during a write operation to Offset 0 with –CE2 low and –CE1 high.

**Table 18: Feature Register**

| Feature Register |    |    |    |    |    |    |    |  |  |

|------------------|----|----|----|----|----|----|----|--|--|

| D7               | D6 | D5 | D4 | D3 | D2 | D1 | D0 |  |  |

### 5.8.2.4 Sector Count Register

27

This registers the number of sectors of data requested to be transferred on a read or write operation between the host and the card. If the value in this register is zero, a count of 256 sectors is specified. If the command was successful, this register is zero at command completion. If not successfully completed, the register contains the number of sectors that need to be transferred in order to complete the request.

**Table 19: Sector Count Register**

| Sector Count Register |    |    |    |    |    |    |    |  |  |

|-----------------------|----|----|----|----|----|----|----|--|--|

| D7                    | D6 | D5 | D4 | D3 | D2 | D1 | D0 |  |  |

### 5.8.2.5 Sector Number Register

This register contains the starting sector number or bits 7-0 of the Logical Block Address (LBA) for lcf9000 data access for the subsequent command.

**Table 20: Sector Number Register**

| Sector Number Register |    |    |    |    |    |    |    |  |  |

|------------------------|----|----|----|----|----|----|----|--|--|

| D7                     | D6 | D5 | D4 | D3 | D2 | D1 | D0 |  |  |

### 5.8.2.6 Cylinder Low Register

This Register contains the low order 8 bits of the starting cylinder address or bits 15-8 of the Logical Block Address.

**Table 21: Cylinder Low Register**

| Cylinder Low Register |    |    |    |    |    |    |    |  |  |  |

|-----------------------|----|----|----|----|----|----|----|--|--|--|

| D7                    | D6 | D5 | D4 | D3 | D2 | D1 | D0 |  |  |  |

### 5.8.2.7 Cylinder High Register

This Register contains the high order 8 bits of the starting cylinder address or bits 23-16 of the Logical Block Address.

**Table 22: Cylinder High Register**

| Cylinder Hig | gh Register |    |    |    |    |    |    |

|--------------|-------------|----|----|----|----|----|----|

| D7           | D6          | D5 | D4 | D3 | D2 | D1 | D0 |

### 5.8.2.8 Device/Head Register

The Drive/Head register is used to select the drive and head. It is also used to select LBA addressing instead of cylinder/head/sector addressing.

Table 23: Device/Head Register

| 1  | LBA | 1  | DRV | HS3 | HS2 | HS1 | HS0 |

|----|-----|----|-----|-----|-----|-----|-----|

| D7 | D6  | D5 | D4  | D3  | D2  | D1  | D0  |

Bit7: this bit is set 1.

**Bit6**: LBA is a flag to select either Cylinder/Head/Sector or Logical Block Address mode. When LBA=0, Cylinder/Head/Sector mode is selected. When LBA=1, Logical Block Address is selected.

Bit5: this bit is set 1.

Bit4: DRV is the drive number. When DRV=0, drive (card) 0 is selected. When DRV=1, drive (card) 1 is

28 Rev 2.1 Datasheet, July. 2012

selected.

**Bit3**: When operation in the Cylinder/Head/Sector mode, this is bit 3 of the head number. It is bit 27 in the Logical Block Address mode.

**Bit2**: When operation in the Cylinder/Head/Sector mode, this is bit 2 of the head number. It is bit 26 in the Logical Block Address mode.

**Bit1**: When operation in the Cylinder/Head/Sector mode, this is bit 1 of the head number. It is bit 25 in the Logical Block Address mode.

**Bit0**: When operation in the Cylinder/Head/Sector mode, this is bit 0 of the head number. It is bit 24 in the Logical Block Address mode.

### 5.8.2.9 Status Register

These registers return the Icf9000 status when read by the host. Reading the Status register does clear a pending interrupt while reading the Auxiliary Status register does not.

Table 24: Status Register

| BUSY | RDY | DWF | DSC | DRQ | CORR | 0  | ERR |

|------|-----|-----|-----|-----|------|----|-----|

| D7   | D6  | D5  | D4  | D3  | D2   | D1 | D0  |

**Bit7**: the busy bit is set when the lcf9000 has access to the command buffer and registers and the host is locked out from accessing the command register and buffer. No other bits in this register are valid when this bit set to a 1.

**Bit6**: RDY indicates whether the device is capable of performing lcf9000 operations. This bit is cleared at power up and remains cleared until the card is ready to accept a command.

**Bit5**: This bit, if set, indicates a write fault has occurred.

Bit4: This bit is set when the Icf9000 is ready.

**Bit3**: The Data Request is set when the Icf9000 requires that information be transferred either to or from the host through the Data register.

During the data transfer of DMA commands, the card shall not asserted DMARD unless either the BUST bit, the DRQ, or both are set to one.

**Bit2**: This bit is set when a Correctable data error has been encountered and the data has been corrected. This condition does not terminate a multi-sector read operation.

Bit1: This bit is always to 0.

29

**Bit0**: This bit is set when the previous command has ended in some type of error. The bits in the Error register contain additional information description the error.

### 5.8.2.10 Device Control Register

This register is used to control the Icf9000 interrupt request and to issue an ATA soft reset to the card. This register can be written even if the device is BUSY.

**Table 25: Device Control Register**

| Х  | Х  | Х  | Х  | Х  | SW Rst | -len | 0  |

|----|----|----|----|----|--------|------|----|

| D7 | D6 | D5 | D4 | D3 | D2     | D1   | D0 |

Bit7-3: These bits are ignored.

**Bit2**: This bit is set to 1 in order to force the Icf9000 to perform a Soft Reset operation. The Card remains in Reset until this bit is reset to '0'.

**Bit1**: the Interrupt Enable bit enables interrupts when the bit is 0. When the bit is 1, interrupt from the Icf9000 are disabled. This bit also controls the Int bit in the Configuration and Status Register. This bit is set to 0 at power on and Reset.

Bit0: This bit is ignored.

### 5.8.2.11 Drive Address Register

This register is provide for compatibility with the AT disk drive interface.

**Table 26: Drive Address Register**

| Х  | -WTG | -HS3 | -HS2 | -HS1 | -HS0 | -Nds1 | -Nds0 |

|----|------|------|------|------|------|-------|-------|

| D7 | D6   | D5   | D4   | D3   | D2   | D1    | D0    |

Bit7: this bit is unknown.

**Bit6**: this bit is – when a write operation is in progress; otherwise, it is 1.

Bit5: this bit is the negation of bit 3 in the Drive/Head register.

Bit4: this bit is the negation of bit 2 in the Drive/Head register.

Bit3: this bit is the negation of bit 1 in the Drive/Head register.

Bit2: this bit is the negation of bit 0 in the Drive/Head register.

Bit1: this bit is 0 when drive 1 is active and selected.

Bit0: this bit is 0 when the drive 0 is active and selected.

### 5.9 Hardware Reset

**Table 27: Timing Diagram, Hardware Reset**

|                            | Item              | Min. | Max. | Normal | Unit |

|----------------------------|-------------------|------|------|--------|------|

| t <sub>SU</sub> (RESET)    | Reset Setup Time  | 20   | -    | -      | ms   |

| t <sub>REC</sub> (VCC)     | -CE Recover       | 1    | -    | -      | us   |

|                            | Time              |      |      |        |      |

| t <sub>PR</sub>            | VCC rising up     | 0.1  | 100  | -      | ms   |

|                            | time              |      |      |        |      |

| t <sub>PF</sub>            | VCC falling down  | 3    | 300  | -      | ms   |

|                            | time              |      |      |        |      |

| t <sub>W</sub> (RESET)     | Reset pulse width | 10   | -    | -      | ms   |

| t <sub>H</sub> (Hi-ZRESET) |                   | 0    | -    | -      |      |

| t <sub>S</sub> (Hi-ZRESET) |                   | 0    | -    | -      |      |

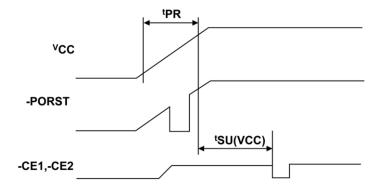

### 5.10 Power on Reset

When the VCC power reaches to 2.7V, the disk drive will be reset.

**Table 28: Timing Diagram, Power On Reset**

|                         | Item                | Min. | Max. | Normal | Unit | Note |

|-------------------------|---------------------|------|------|--------|------|------|

| t <sub>SU</sub> (RESET) | -CE Setup Time      | 20   | -    | -      | ms   |      |

| t <sub>PR</sub>         | -VCC Rising Up Time | 0.1  | 100  | -      | ms   |      |

### **Power on Reset Timing**

Figure 4: Timing Diagram, Power On Reset

31 Rev 2.1 Datasheet, July. 2012

### **5.11 Support IDE Commands**

Icf9000 supports the commands listed in Table 29.

**Table 29: IDE Commands**

| Command                   | Code | FR | sc | SN | CY | DH | LBA |

|---------------------------|------|----|----|----|----|----|-----|

| Check Power Mode          | E5H  | -  | -  | -  | -  | D  | -   |

| Execute Device Diagnostic | 90H  | -  | -  | -  | -  | D  | -   |

| Flush Cache               | E7H  | -  | -  | -  | -  | Υ  | -   |

| Identify Device           | ECH  | -  | -  | -  | -  | D  | -   |

| Idle                      | E3H  | -  | Υ  | -  | -  | D  | -   |

| Idle immediate            | E1H  | -  | -  | -  | -  | D  | -   |

| Read Buffer               | E4H  | -  | -  | -  | -  | D  | -   |

| Read DMA                  | C8H  | -  | Υ  | Υ  | Υ  | Υ  | Υ   |

| Read Sector(s)            | 20H  | -  | Υ  | Υ  | Υ  | Υ  | Υ   |

| Read Verify Sector(s)     | 40H  | -  | Υ  | Υ  | Υ  | Υ  | Υ   |

| Set Features              | EFH  | Υ  | -  | -  | -  | D  | -   |

| Set Multiple Mode         | C6H  | -  | Υ  | -  | -  | D  | -   |

| Set Sleep Mode            | E6H  | -  | -  | -  | -  | D  | -   |

| SMART                     | B0h  | Υ  | -  | -  | Υ  | Υ  | -   |

| Standby                   | E2H  | -  | -  | -  | -  | D  | -   |

| Standby Immediate         | E0H  | -  | -  | -  | -  | D  | -   |

| Write Buffer              | E8H  | -  | -  | -  | -  | D  | -   |

| Write DMA                 | CAH  | -  | Υ  | Υ  | Υ  | Υ  | Υ   |

| Write Multiple            | C5h  | -  | Υ  | Υ  | Υ  | Υ  | Υ   |

| Write Sector(s)           | 30H  | -  | Υ  | Υ  | Υ  | Υ  | Υ   |

### **Defines:**

FR: Feature Register

SC: Sector Count Register

SN: Sector Number Register

CY: Cylinder Registers

32

DH: Card/Device/Head Register

LBA: LBA Block Address Mode Supported

Y: The register contains a valid parameter for this command. For Card/Device/Head Register Y means both the CompactFlash Storage Card and head parameter are used; D – only the CompactFlash Storage Card parameter is valid and not the head parameter; C – The register contains command specific data (see command description for use).

### 5.11.1 Check power mode -E5h

Table 30: Check power mode information

| Register         | 7   | 6 | 5 | 4     | 3 | 2 | 1 | 0 |

|------------------|-----|---|---|-------|---|---|---|---|

| Command(7)       | E5h |   |   |       |   |   |   |   |

| C/D/H(6)         | Х   |   |   | Drive | Χ |   |   |   |

| Cylinder High(5) | Χ   |   |   |       |   |   |   |   |

| Cylinder Low(4)  | Χ   |   |   |       |   |   |   |   |

| Sector Number(3) | Χ   |   |   |       |   |   |   |   |

| Sector Count(2)  | Χ   |   |   |       |   |   |   |   |

| Feature(1)       | Χ   |   |   |       |   |   |   |   |

This command checks the power mode. If the CompactFlash Storage is in, going to, or recovering from the sleep mode, the CompactFlash Storage Card sets BSY, sets the Sector Count Register to 00h, clears BSY and generates an interrupt. If the ompactFlash Storage Card is in idle mode, the CompactFlash Storage Card sets BSY, sets the Sector Count Register to FFh, clears BSY and generates an interrupt.

### 5.11.2 Execute Device Diagnostic - 90h

Table 31: Execute device diagnostic information

| Register         | 7   | 6 | 5 | 4     | 3 | 2 | 1 | 0 |

|------------------|-----|---|---|-------|---|---|---|---|

| Command(7)       | 90h |   |   |       |   |   |   |   |

| C/D/H(6)         | Χ   |   |   | Drive | Χ |   |   |   |

| Cylinder High(5) | Χ   |   |   |       |   |   |   |   |

| Cylinder Low(4)  | Χ   |   |   |       |   |   |   |   |

| Sector Number(3) | Χ   |   |   |       |   |   |   |   |

| Sector Count(2)  | Χ   |   |   |       |   |   |   |   |

| Feature(1)       | Χ   |   |   |       |   |   |   |   |

This command performs the internal diagnostic tests implemented by the CompactFlash Storage Card. When the diagnostic command is issued in the True IDE Mode, the Drive bit is ignored and the diagnostic command is executed by both the Master and the Slave with the Master responding with status for both devices. The Diagnostic codes are shown in Table 34. Diagnostic Codes are returned in the Error Register at the end of the command.

**Table 32: Diagnostic**

| Code | Error Type             |

|------|------------------------|

| 01h  | No Error Detected      |

| 02h  | Formatter Device Error |

| 03h  | Sector Buffer Error    |

| 04h  | ECC Circuitry Error    |

Rev 2.1 Datasheet, July. 2012

| 05h | Controller Microprocessor Error |

|-----|---------------------------------|

| 8Xh | Slave Error in True IDE Mode    |

### 5.11.3 Flush Cache- E7h

5.11.18.1 Command Code

E7h

5.11.18.2 Protocol

Non-data

5.11.18.3 Inputs

Table 33: Flush cache command for inputs information

| Register     | 7   | 6  | 5   | 4   | 3  | 2 | 1 | 0 |

|--------------|-----|----|-----|-----|----|---|---|---|

| Features     | Na  |    |     |     |    |   |   |   |

| Sector Count | Na  |    |     |     |    |   |   |   |

| LBA Low      | Na  |    |     |     |    |   |   |   |

| LBA Mid      | Na  |    |     |     |    |   |   |   |

| LBA High     | Na  |    |     |     |    |   |   |   |

| Device       | obs | Na | obs | DEV | Na |   |   |   |

| Command      | E7h |    |     |     |    |   |   |   |

Device register-

**DEV** shall specify the selected device.

### 5.11.18.4 Normal Output

Table 34: Flush cache command for normal output information

| Register     | 7   | 6    | 5   | 4   | 3   | 2  | 1  | 0   |